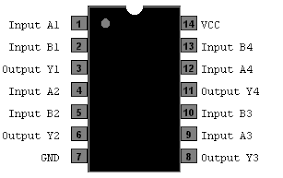

El 74LS32 es un circuito integrado de compuerta OR de cuatro entradas. Una compuerta OR tiene una o más entradas y una salida. Si al menos una de las entradas es 1, entonces la salida será 1. Si todas las entradas son 0, entonces la salida será 0. La 74LS32 es una compuerta OR de cuatro entradas, lo que significa que tiene cuatro entradas y una salida. Se utiliza para realizar la operación lógica OR en un circuito digital.Cuando todas sus entradas están en 0 (cero) o en BAJA, su salida está en 0 o en BAJA, mientras que cuando al menos una o ambas entradas están en 1 o en ALTA, su SALIDA va a estar en 1 o en ALTA. En otro sentido, la función de la compuerta OR efectivamente encuentra el máximo entre dos dígitos binarios, así como la función AND encuentra el mínimo. Se puede ver claramente que la salida X solamente es «0» (0 lógico, nivel bajo) cuando la entrada A como la entrada B están en «0». En otras palabras la salida X es igual a 0 cuando la entrada A y la entrada B son 0. Este dispositivo realiza la función booleana Y = A + B o Y = (A \ • B \) \ en lógica positiva.